Das macht man üblicherweise über GPIO0. Oder halt einen externen Oszillator. Also interessant ist der IC auf jeden Fall, mir gefallen die Datasheets von TI auch gut, weil sie beim PCB-Layout auch viele wertvolle Infos geben. Aber man müsste einen Treiber halt dafür schreiben.

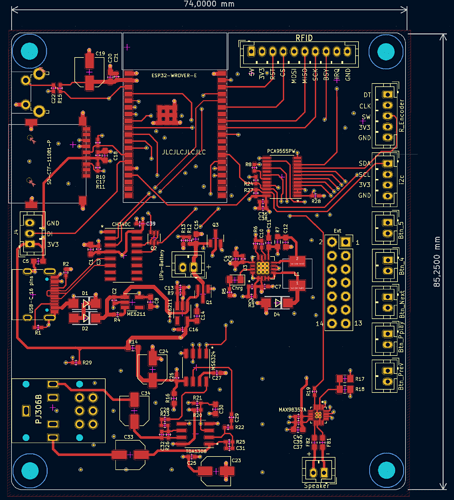

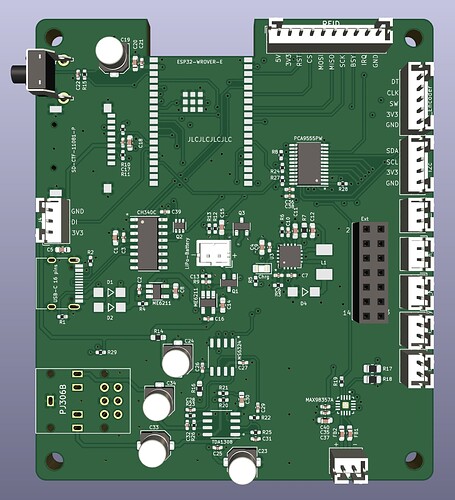

Von daher, und weil ich halt auch noch gut 70 MS6324 hier habe, bin ich jetzt erstmal wieder bei MAX vs MS6324+TDA1308 geblieben. Ich habe jetzt einen zweiten PCB geplant, der vier Layer nutzt. Zum ersten Mal habe ich auch richtig viel Arbeit reingesteckt und das Ganze von Hand geroutet. Ein Layer ist komplett für GND, so dass man alle GND-Punkte mit Vias anbindet und nicht mehr routen muss. Ich habe drauf geachtet, die Entkoppelkondensatoren immer schön nah an die ICs zu setzen und bin mit der SMD-Größe runter auf größtenteils 0402 und teilweise 0603. So ist das schön kompakt geworden, allerdings werde ich für das erste Testboard die ganz kleinen Bauteile direkt von JLC auch löten lassen.

Layer 1

3d-Ansicht

Das ist jetzt, wie beim letzten Mal, erstmal nur die LiPo-Variante. Wird also noch ein bisschen dauern.

Hoffe mal, dass ich damit die Probleme beim SD-Zugriff beseitigen kann.